Bienvenue à l'ENSEIRB-MATMECA

L'ENSEIRB-MATMECA est une école d'ingénieurs de Bordeaux INP

L’Ecole Nationale Supérieure d’Electronique, Informatique, Télécommunications, Mathématique et Mécanique de Bordeaux est une école d’ingénieurs publique, formant des ingénieurs à fortes compétences scientifiques et techniques, prêts à répondre aux grands enjeux du monde numérique.

Devenir ingénieur

Découvrir l'ENSEIRB-MATMECA

International

Espace entreprise

Actualités

Agenda

Témoignages

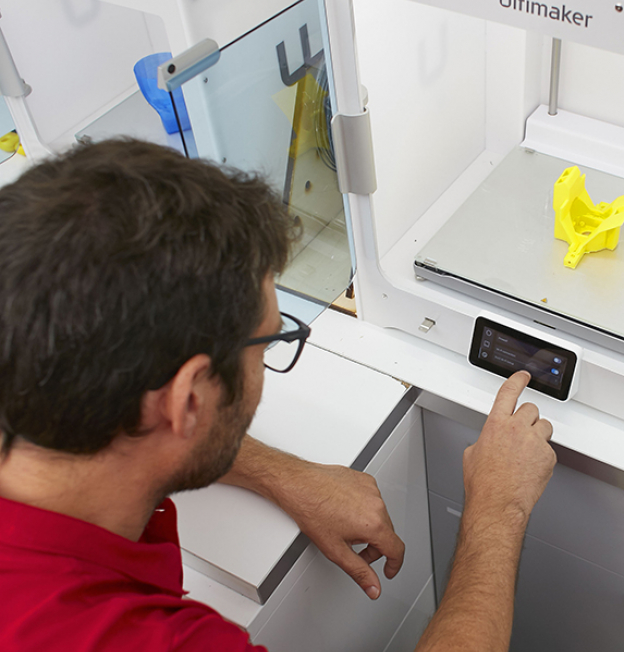

[Innovation] (Re)découvrez le FabLab et EirLab Community

[ENSTBB] Le parcours « Biotechnologies & Production de protéines thérapeutiques » fête ses 10 ans

[Relations Internationales] Découvrez les témoignages de nos étudiants autour du monde

[Bordeaux INP] Rencontrez Marwan Zizi, le Vice-Président Élève-Ingénieur de Bordeaux INP

Admissions

L’ENSEIRB-MATMECA recrute ses élèves-ingénieurs à niveau BAC +2.

Pour intégrer l'école, plusieurs voies d'admissions sont possibles : après une classe préparatoire MP/PC/PSI/TSI/PT via le Concours Commun INP (CCINP), après une classe préparatoire intégrée (La Prépa des INP, CPBx, Licence renforcée de Poitiers) ou sur titres (après un DUT, un BTS ou une licence).

Choisissez la voie la plus adaptée à votre profil !